# A 1V 3.8-5.7 GHz Differentially-Tuned VCO in SOI CMOS

Neric Fong<sup>1</sup>, Jean-Olivier Plouchart<sup>2</sup>, Noah Zamdmmer<sup>3</sup>, Duixian Liu<sup>2</sup>, Lawrence Wagner<sup>3</sup>,

Calvin Plett<sup>1</sup> and Garry Tarr<sup>1</sup>

<sup>1</sup>Department of Electronics, Carleton University, Ottawa, Ontario, Canada K1S 5B6

<sup>2</sup>IBM T.J. Watson Research Center, Yorktown Heights, NY 10598

<sup>3</sup>IBM Microelectronics Semiconductor Research and Development Center, Hopewell Junction, NY 12533

**Abstract** – A 1 V 3.8-5.7 GHz VCO was designed and fabricated in a 0.13  $\mu$ m SOI CMOS process [1]. This VCO features differentially-tuned accumulation MOS varactors that (a) provides 40% frequency tuning when biased between 0 to 1 V, and (b) rejects common-mode noise such as flicker noise. At 1 MHz offset, the phase noise is -121.67 dBc/Hz at 3.8 GHz, and -111.67 dBc/Hz at 5.7 GHz. The power dissipation is between 2.3 to 2.7 mW depending on the centre frequency. When  $V_{DD}$  is reduced to 0.75 V, the VCO only dissipates 0.8 mW at 5.5 GHz.

## I. INTRODUCTION

As modern CMOS technology feature size is scaled down to deep-submicron, the supply voltage  $V_{DD}$  has to decrease in proportion. One of the main reasons is the low breakdown voltage due to gate oxide thinning, which is required to maintain short-channel effects at an acceptable level. The downscaling of  $V_{DD}$  imposes many design challenges to analog/RF designs [2], and the VCO is no exception. The most obvious problem is the reduction of voltage swing, which lowers the output power and degrades the phase noise. This can be partially resolved by using complementary topology to improve the phase noise [3].

Another problem, which is often overlooked, is the frequency tuning range. Limited frequency tuning is one of the bottlenecks that hinders commercialization of the CMOS VCO. The accumulation MOS (AMOS) varactor [4] offers a solution to this problem. High-Q AMOS varactors giving  $C_{max}/C_{min}$  of 5 with  $\pm 1$  V tuning voltage have been demonstrated in a 0.13  $\mu$ m SOI CMOS technology [1]. A VCO with more than 50% frequency tuning was measured [5] using this technology. However, high  $C_{max}/C_{min}$  ratio over low voltage tuning range implies high varactor gain  $k_v$  (and hence VCO gain  $k_{vco}$ ), which is unfavourable to phase noise performance [6].

In this paper, a simple theory will be introduced to explain how varactors upconvert low-frequency common-mode noise, such as flicker noise, near the carrier, and how the differentially-tuned varactors can be used to suppress such upconversion. The theory will be verified by measurement.

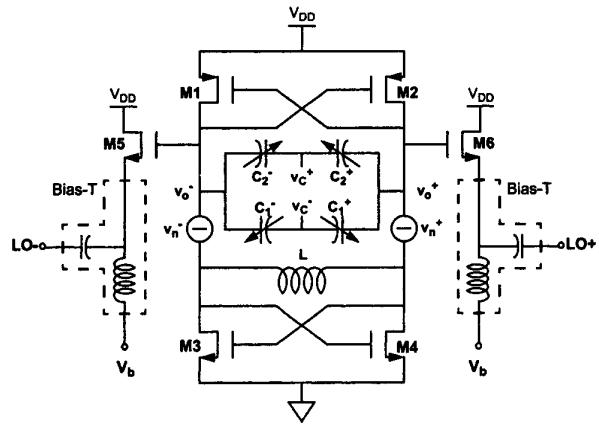

Fig. 1. Schematic of Differentially-Tuned VCO.  $v_n^+$  and  $v_n^-$  are noise sources from each branch.

## II. VARACTOR NOISE ANALYSIS

### A. Low-Frequency Noise Upconversion

One mechanism for upconversion of low-frequency noise, such as flicker noise, is the non-linearity of the circuit [3]. However, the low-frequency noise can also modulate the varactor directly and this is seen as jitter near the carrier. Consider a complementary LC-VCO as shown in Fig. 1. The resonator consists of the inductor  $L$  and the capacitor  $C$ , which consists of  $C_1^+$ ,  $C_1^-$ ,  $C_2^+$  and  $C_2^-$ . The resonant frequency  $\omega_o$  is given by

$$\omega_o = \frac{1}{\sqrt{LC}} \quad (1)$$

Consider  $v_n^+$  and  $v_n^-$  as the total noise from the transistors at each side as shown in Fig. 1. At low frequency, the inductor  $L$  behaves like a short-circuit, so

$$v_n^+ = v_n^- \quad (2)$$

Therefore, all the noise power at low frequency can be considered as common-mode noise, defined as  $v_{ncm}$ . One mechanism for low-frequency noise upconversion is that  $v_{ncm}$  injects into the varactor through the nodes  $v_o^+$  and  $v_o^-$ . This

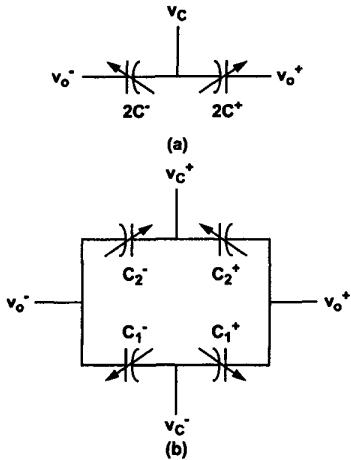

Fig. 2. (a) Single-Ended and (b) Differentially-Tuned Varactor

noise is subsequently upconverted to the carrier frequency by the resonator, contributing to the phase noise of the VCO. Mathematically, the expression for  $C$  in (1) is

$$C = C_0 + k_v(v_{tune} + v_{ncm}) \quad (3)$$

where  $C_0$  is the zero bias capacitance,  $k_v$  is the varactor gain, and  $v_{tune}$  is the voltage across the varactor. Equation (3) clearly shows that  $C$  is modulated by  $v_{ncm}$ , and the higher the  $k_v$ , the higher the low-frequency noise injection. Therefore, many VCOs have the worst phase noise in the middle of the tuning range where  $k_v$  is the highest. Meanwhile, the best phase noise usually occurs at the boundaries of the tuning range where  $k_v$  is minimum. As the power supply scales down, the varactor gain  $k_v$  becomes large in order to maintain the same tuning range. Therefore, this upconversion mechanism is critical for low-voltage VCO.

#### B. Single-ended vs. Differentially Tuned Varactor

In this section, common-mode noise rejection in the differentially-tuned varactor will be analyzed. The effect of common-mode noise in single-ended tuned varactors is first analyzed starting from the varactor topology given in Fig. 2a. To demonstrate common-mode noise rejection, the equivalent capacitance  $C$  between  $v_C$  and  $v_o^+$  is calculated. From (3), it is given by

$$C = 2C^+ = 2C_0 + 2k_v(v_C + v_{ncm}) \quad (4)$$

Hence, the common-mode noise modulates the varactor, which will result in jitter and phase noise. If the varactor is differentially-tuned as shown in Fig. 2b, then the capacitances are given by  $v_C^+$ ,  $v_C^-$  and  $v_o^+$  such that

$$C_1^+ = C_0 + k_{v1}(v_C^+ + v_{ncm}) \quad (5)$$

$$C_2^+ = C_0 - k_{v2}(v_C^- + v_{ncm}) \quad (6)$$

Since  $C = C_1^+ + C_2^+$ , if the varactor is perfectly symmetrical

such that  $k_{v1} = -k_{v2}$ , the expression for  $C$  is

$$C = 2C_0 + 2k_v v_C \quad (7)$$

where  $v_C$  is  $v_C^+ - v_C^-$ . If  $|k_{v1}|$  and  $|k_{v2}|$  are not the same, the gain of the common-mode noise is reduced to  $|k_{v1}| - |k_{v2}|$ . Therefore, it has been shown that differential tuning can be used to reject common-mode noise, such as flicker noise and shot noise.

### III. IMPLEMENTATION AND MEASUREMENT

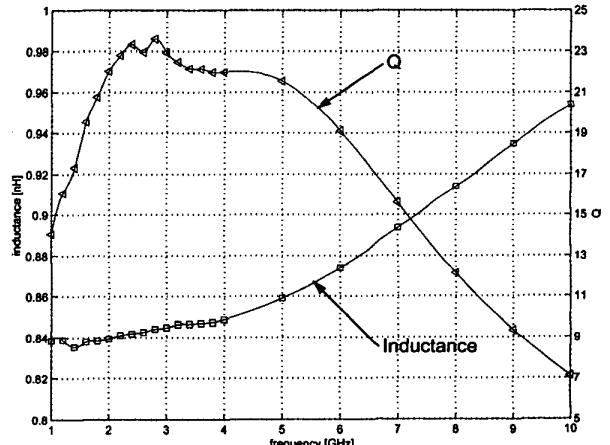

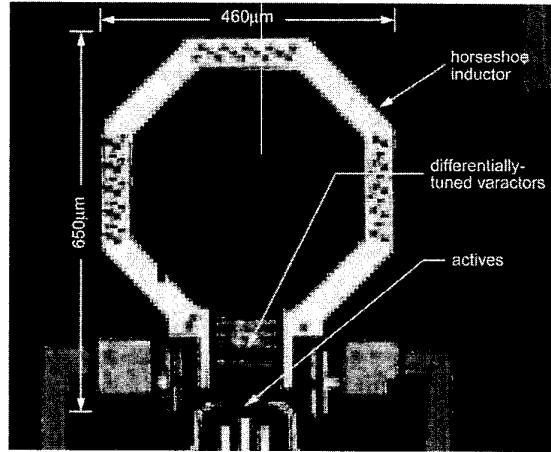

As shown in Fig. 1, the VCO is an LC cross-coupled differential circuit with both PMOS and NMOS latches, which generate negative resistance to cancel losses in the LC resonator. The monolithic inductor is a horseshoe shaped single loop with a diameter of 460  $\mu\text{m}$  as shown in the micrograph (Fig. 9). The measured inductance is 0.85 nH and  $Q$  is above 20 between 3.8 and 5.7 GHz as shown in Fig. 3. The AMOS varactors are differentially tuned for common-mode noise rejection. Bias-T source followers are used as the output buffers. The inductive choke inside the bias-T is used to provide high ac impedance, so that small transistors can be used to provide enough output current drive without loading the VCO core heavily.

#### A. Frequency Tuning

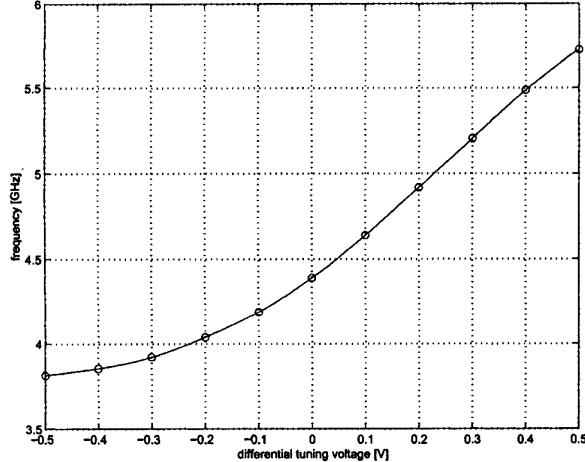

The VCO was measured using on-wafer probing together with a 26.5 GHz HP8563 spectrum analyser with a phase noise module. The frequency vs. varactor tuning voltage at 1 V  $V_{DD}$  is shown in Fig. 4. The differential tuning voltage  $v_{dtune}$  is related to  $v_C^+$  and  $v_C^-$  by

$$v_C^{+/-} = (V_{DD}/2) \pm v_{dtune} \quad (8)$$

For example, if  $v_{dtune} = 0$  V, then  $v_C^+ = 0.5$  V and  $v_C^- = 0.5$  V. If  $v_{dtune} = -0.5$  V, then  $v_C^+ = 0$  V and  $v_C^- = 1$  V. For a tuning voltage from 0 to 1 V, the carrier frequency can be tuned from 3.812 GHz to 5.716 GHz, achiev-

Fig. 3. Measured Inductance and Q (Single-Ended) vs. Frequency

Fig. 4. Frequency vs. Tuning Voltage at 1V  $V_{DD}$

ing 40% tuning range. This wide tuning range is made possible by the reduced parasitic due to the buried oxide of SOI that minimizes junction capacitance, and improved lithography that reduces overlap capacitance.

#### B. Common-Mode Rejection

At 1 V  $V_{DD}$ , common-mode voltage was applied such that  $v_C^+ = v_C^-$ , and the result is summarized in Table I.

TABLE I. Common-Mode Performance Measurement

| $v_C^+ = v_C^-$ | $f_c$     | phase noise @ 1 MHz |

|-----------------|-----------|---------------------|

| 0.0 V           | 4.492 GHz | -117.00 dBc/Hz      |

| 0.5 V           | 4.401 GHz | -117.83 dBc/Hz      |

| 0.6 V           | 4.404 GHz | -118.33 dBc/Hz      |

| 1.0 V           | 4.475 GHz | -118.50 dBc/Hz      |

The frequency variation is within 2%, while the phase noise variation is within  $\pm 1$  dB. Therefore, it is concluded that the varactors are highly symmetrical, which should result in good common-mode noise rejection.

#### C. Phase Noise

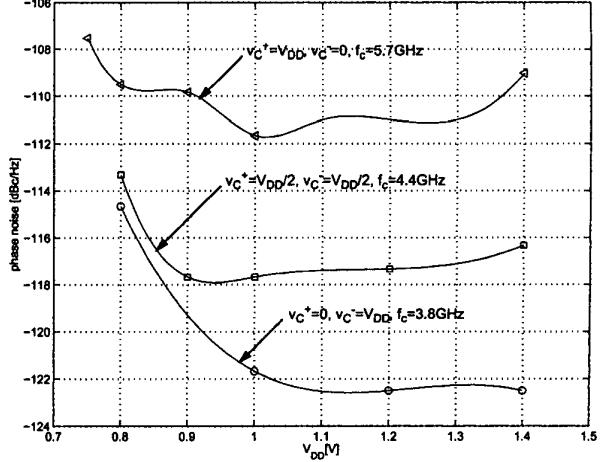

The phase noise was measured at several different frequencies across the wide tuning range. At 1 V  $V_{DD}$ , the best phase noise is -121.67 dBc/Hz at 1 MHz offset, measured at the lower frequency bound (3.812 GHz at  $v_{dtune} = -0.5$  V) where the VCO gain is minimal and the inductor  $Q$  is near its peak. At the middle of the range (4.4 GHz at  $v_{dtune} = 0$ ),  $k_v$  is high and the phase noise is -117.83 dBc/Hz at 1 MHz offset. At the upper end of the tuning range (5.716 GHz at  $v_{dtune} = 0.5$ ), the phase noise is -111.67 dBc/Hz at 1 MHz offset. The phase noise was also measured for  $V_{DD}$  between

Fig. 5. Phase Noise vs.  $V_{DD}$

0.75 V and 1.4 V, and the result is summarized in Fig. 5.

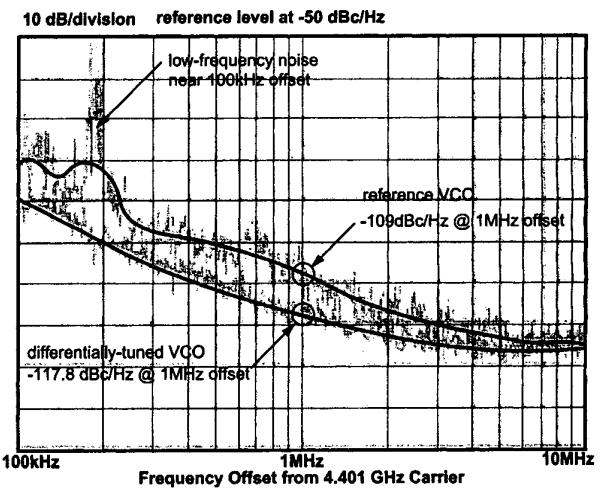

To evaluate the phase noise improvement over a conventional single-ended tuning scheme, a reference VCO with varactor topology as shown in Fig. 2a was fabricated and measured. At 4.4 GHz, with both VCOs operating in the high  $k_v$  region (middle of the tuning range), the phase noise was measured and compared as shown in Fig. 6. At 1 MHz offset, the differential-tuning topology improves the phase noise by about 9 dB. Due to common-mode rejection, the upconverted low-frequency noise near the 100 kHz offset is filtered out, offering a cleaner frequency spectrum. Furthermore, reduction in noise implies that less current is required for the VCO to oscillate. The differentially-tuned VCO can be operated at 0.75 V  $V_{DD}$ , drawing only 0.8 mW at 5.5 GHz. Meanwhile, the reference VCO can only operate down to 0.83 V, drawing about 1 mW at that frequency.

Fig. 6. Phase Noise Comparison at 4.4 GHz

#### D. FOM and Power Dissipation

A widely used figure of merit (FOM) for VCO performance is defined as

$$FOM = L\{f_{off}\} - 20\log(f_c/f_{off}) + 10\log(P_{dc}) \quad (9)$$

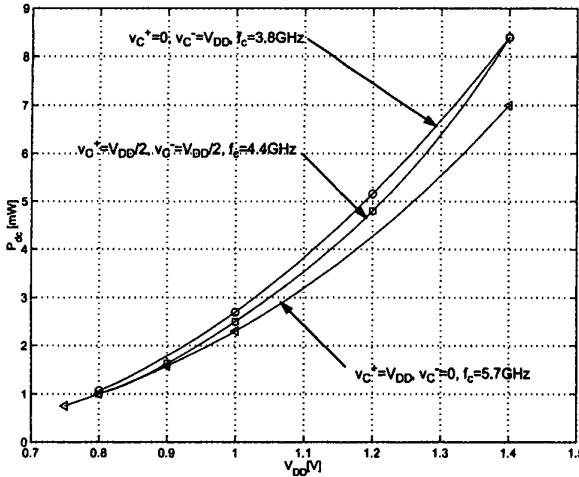

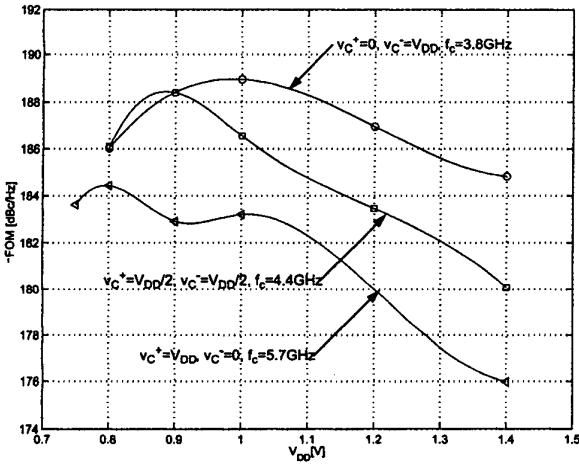

where  $L\{f_{off}\}$  is the measured phase noise at the frequency offset  $f_{off}$  from the carrier at  $f_c$ , and  $P_{dc}$  is the measured DC power dissipation in mW (Fig. 7). The result is plotted in Fig. 8. The lowest power dissipation is achieved at 0.75 V  $V_{DD}$ , where only 0.8 mW of power is drawn at 5.5 GHz. To the authors' knowledge, this VCO has the lowest power dissipation compared to any published CMOS VCOs at this frequency. Meanwhile, the best FOM is -189 dBc/Hz at 1 V  $V_{DD}$ .

Fig. 7. Power Dissipation vs.  $V_{DD}$

Fig. 8. Figure of Merit vs  $V_{DD}$

#### IV. CONCLUSION

In this article, a 1 V 3.8-5.7 GHz differentially-tuned com-

plementary LC-VCO with 40% tuning range was designed and fabricated using the IBM 0.13  $\mu$ m SOI CMOS technology. The VCO has demonstrated that differentially-tuned varactors can provide wide tuning range and reject common-mode noise. At 1 MHz offset, the nominal phase noise (4.4 GHz at  $v_{dtune} = 0$ ) is -117.83 dBc/Hz, and the FOM is 187 dBc/Hz. The power consumption is between 2.3-2.7 mW, and the buffered output power is -9 dBm. If the VCO is operated at 0.75 V  $V_{DD}$ , the circuit only draws 0.8 mW of power, the lowest power dissipation compared to any published CMOS VCO. The VCO occupies a total area of 650  $\mu$ m by 460  $\mu$ m excluding the pads, as shown in the micrograph Fig. 9.

Fig. 9. Micrograph of Differentially-Tuned VCO

#### ACKNOWLEDGMENT

We would like to thank D. Friedman, M. Soyuer, M. Oprysko, F. Assaderaghi, G. Shahidi of IBM, and J. Rogers of Carleton University for their advice and support.

#### REFERENCES

- [1] N. Zamdmer, A. Ray, J.-O. Plouchart, L. Wagner, N. Fong, K. Jenkins, W. Jin, P. Smeys, I. Yang, G. Shahidi, F. Assaderaghi, "A 0.13  $\mu$ m SOI CMOS Technology for Low-power Digital and RF Application," *IEEE Symposium on VLSI Technology*, 2001.

- [2] D. Buss, "Device issues in the integration of Analog/RF functions in deep submicron digital CMOS," *IEEE International Electron Devices Meeting Tech. Digest*, pp. 423-426, 1999.

- [3] A. Hajimiri and T. H. Lee, "Design Issues in CMOS Differential LC Oscillators," *IEEE J. Solid-State Circuits*, vol. 34, pp. 717-724, May 1999.

- [4] P. Andreani, "On the use of MOS Varactors in RF VCO's," *IEEE J. Solid-State Circuits*, vol. 35, pp. 905-910, June 2000.

- [5] N. Fong, J.-O. Plouchart, N. Zamdmer, D. Liu, L. Wagner, C. Plett and G. Tarr, "A Low-Voltage Multi-GHz VCO with 58.7% Tuning Range in SOI CMOS," accepted in *IEEE Custom Integrated Circuits Conf.* 2002.

- [6] U. L. Rohde, D. P. Newkirk, *RF/Microwave Circuit Design for Wireless Applications*, Wiley Interscience, p. 737, 2000.